## **Processor security**

# The processor

Part of the trusted computing base (TCB):

but is optimized for performance,

... security may be secondary

Processor design and security:

- Important security features, such as hardware enclaves

- Some features can be exploited for attacks:

- Speculative execution, transactional memory, ...

- An active area of research!

### Intel SGX

### An overview

(Software Guard eXtensions)

Stanford | Center for | Stanford | Professional Development

### SGX: Goals

Extension to Intel processors that support:

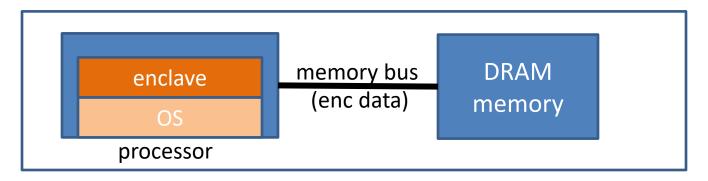

- Enclaves: running code and memory <u>isolated</u> from the rest of system

- Attestation: prove to local/remote system what code is running in enclave

- Minimum TCB: only processor is trusted nothing else: DRAM and peripherals are untrusted ⇒ all writes to memory are encrypted

# Applications

#### Server side:

- Storing a Web server HTTPS secret key: secret key only opened inside an enclave ⇒ malware cannot get the key

- Running a private job in the cloud: job runs in enclave Cloud admin cannot get code or data of job

### **<u>Client side</u>**:

• Hide anti-virus (AV) signatures:

AV signatures are only opened inside an enclave not exposed to adversary in the clear

### Intel SGX: how does it work?

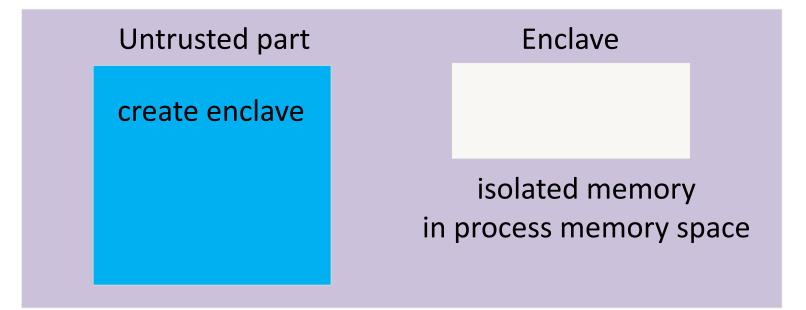

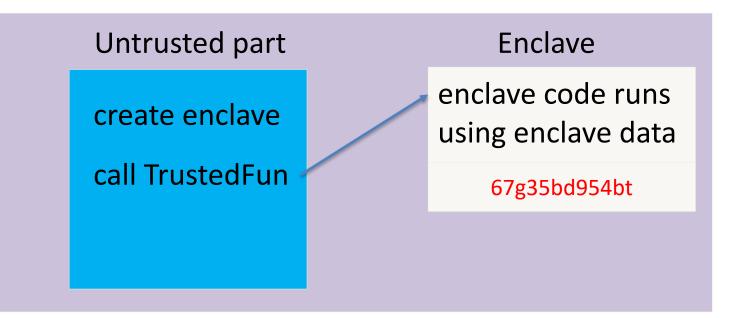

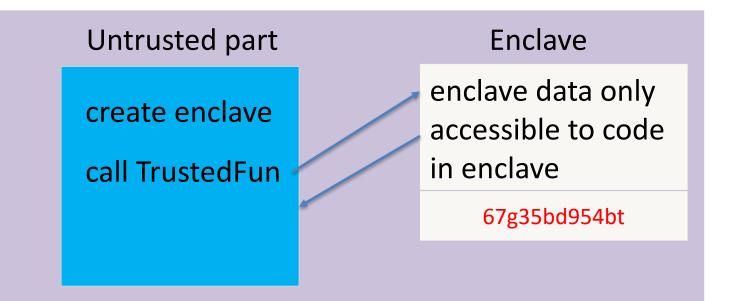

An application defines part of itself as an enclave

#### An application defines part of itself as an enclave

An application defines part of itself as an enclave

An application defines part of itself as an enclave

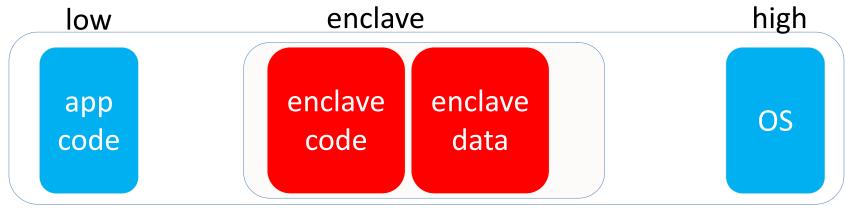

Part of process memory holds the enclave:

- Enclave code and data are written encrypted to main memory

- Processor prevents access to cached enclave data outside of enclave.

### Creating an enclave: new instructions

Enclave init code loaded as cleartext

- **ECREATE**: establish memory address for enclave

- EADD: copies memory pages into enclave <-

- **EEXTEND:** computes hash of enclave contents (256 bytes at a time)

- EINIT: verifies that hashed content is properly signed if so, initializes enclave (signature = RSA-3072)

- **EENTER**: call a function inside enclave

- **EEXIT**: return from enclave

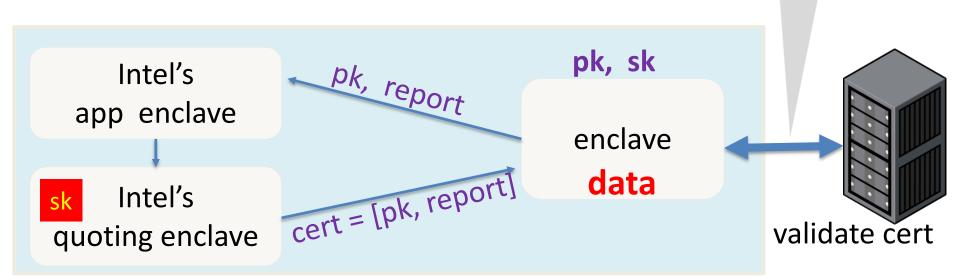

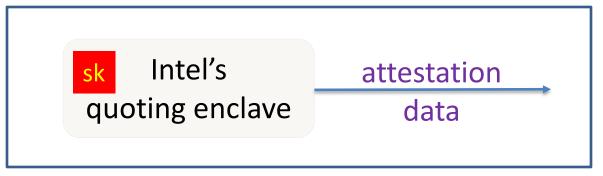

### Provisioning enclave with secrets: attestation

The problem: enclave memory is in the clear prior to activation (EINIT)

E(pk, data)

(code)

• How to get secrets into enclave?

Remote Attestation (simplified): report: contains h

## Summary

SGX: an architecture for managing secret data

- Intended to process data that cannot be read by anyone, except for code running in enclave

- Attestation: proves what code is running in enclave

- Minimal TCB: nothing trusted except for x86 processor

- Not suitable for legacy applications

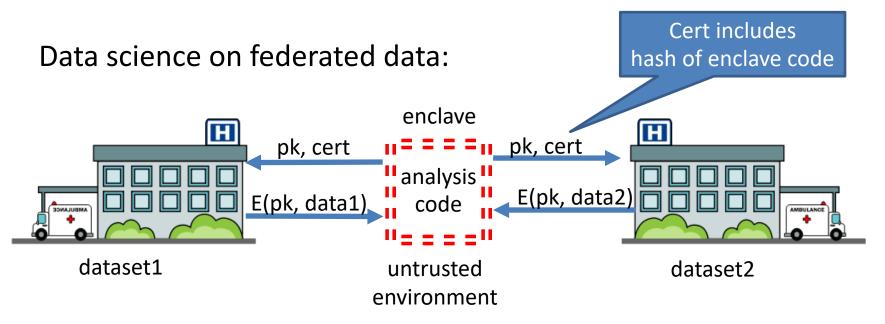

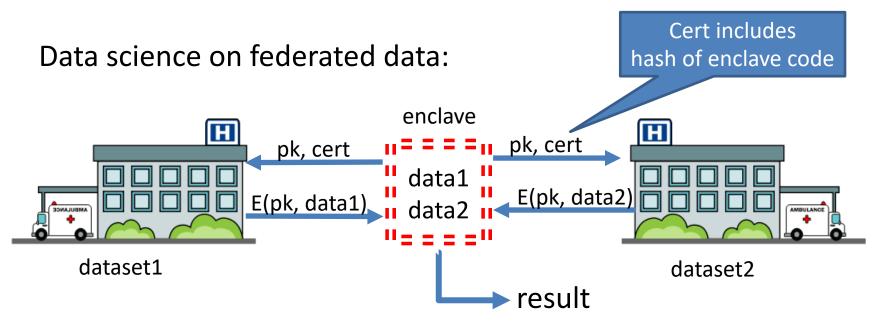

### An example application

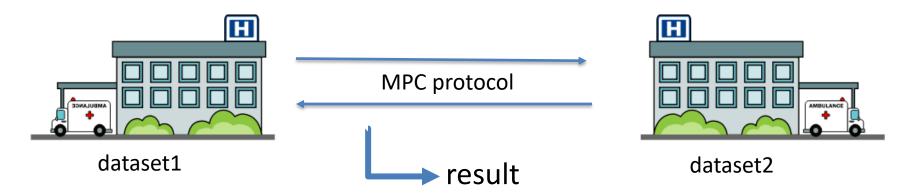

Data science on federated data:

Can we run analysis on union(dataset1, dataset2) ??

For simple computations, can use multiparty computation (MPC)

### An example application

For more complex analysis, can use (secure) hardware enclave

### An example application

For more complex analysis, can use (secure) hardware enclave

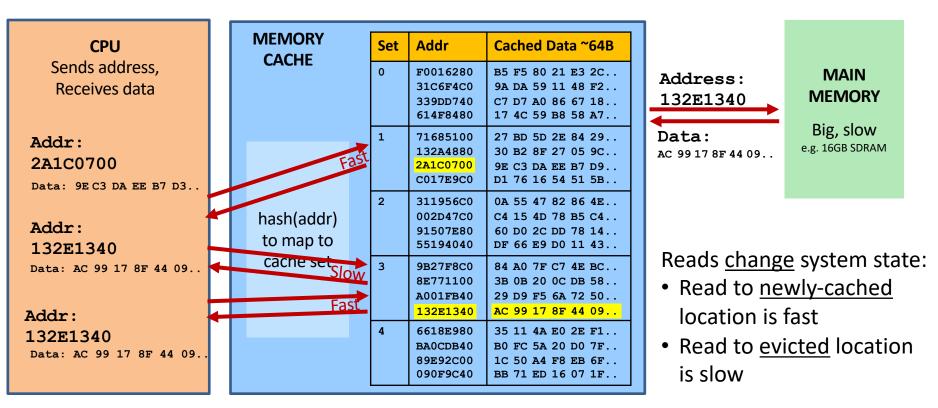

# SGX insecurity: (1) side channels

Attacker controls the OS. OS sees lots of side-channel info:

- Memory access patterns

- State of processor caches as enclave executes

- State of branch predictor

All can leak enclave data. Difficult to block.

### SGX insecurity: (2) extract quoting key

Attestation: proves to 3<sup>rd</sup> party what code is running in enclave

• Quoting **sk** stored in Intel enclave on untrusted machines

What if attacker extracts **sk** from <u>some</u> quoting enclave?

Can attest to arbitrary non-enclave code

... see Foreshadow attack and Intel's response

### The Spectre attack

#### Speed vs. security in HW

[slides credit: Paul Kocher]

# Performance drives CPU purchases

Clock speed maxed out:

- Pentium 4 reached 3.8 GHz in 2004

- Memory latency is slow and not improving much

To gain performance, need to do more per cycle!

- Reduce memory delays  $\rightarrow$  caches

- Work during delays  $\rightarrow$  speculative execution

### Memory caches (4-way associative)

Caches hold local (fast) copy of recently-accessed 64-byte chunks of memory

### Speculative execution

CPUs can guess likely program path and do speculative execution

• Example:

if (uncached\_value == 1) // load from memory a = compute(b)

- Branch predictor guesses if() is 'true' (based on prior history)

- Starts executing compute(b) speculatively

- When value arrives from memory, check if guess was correct:

- **Correct**: Save speculative work  $\Rightarrow$  performance gain

- **Incorrect**: Discard speculative work  $\Rightarrow$  no harm ????

#### **Architectural Guarantee**

Register values eventually match result of in-order execution

#### **Speculative Execution**

CPU regularly performs incorrect calculations, then deletes mistakes

#### Is making + discarding mistakes the same as in-order execution?

The processor executed instructions that were not supposed to run !!

The problem: instructions can have observable side-effects

if (x < array1\_size)

y = array2[ array1[x]\*4096 ];</pre>

Suppose unsigned int x comes from untrusted caller

### Execution without speculation is safe: array2[array1[x]\*4096] not eval unless x < array1\_size</pre>

What about with speculative execution?

if (x < array1\_size)

y = array2[array1[x]\*4096];</pre>

#### **Before attack:**

- Train branch predictor to expect if() is true (e.g. call with x < array1\_size)</li>

- Evict array1\_size and array2[] from cache

#### Memory & Cache Status

array1\_size = 00000008

Memory at array1 base:

8 bytes of data (value doesn't matter)

Memory at array1 base+1000:

**09** F1 98 CC 90... (something secret)

| array2[  | 0*4096]  |   |                  |                     |

|----------|----------|---|------------------|---------------------|

| array2[  | 1*4096]  |   |                  |                     |

| array2[  | 2*4096]  |   |                  |                     |

| array2[  | 3*4096]  |   |                  |                     |

| array2[  | 4*4096]  |   |                  |                     |

| array2[  | 5*4096]  |   |                  |                     |

| array2[  | 6*4096]  | ≻ | Contents don't n | natter              |

| array2[  | 7*4096]  |   | only care about  | cache <i>status</i> |

| array2[  | 8*4096]  |   | Uncached         | Cached              |

| array2[  | 9*4096]  |   | Uncacheu         | Cacilleu            |

| array2[1 | L0*4096] |   |                  |                     |

| array2[1 | L1*4096] |   |                  |                     |

| •••      | J        |   |                  |                     |

if (x < array1\_size)

y = array2[array1[x]\*4096];</pre>

Attacker calls victim with x=1000

Speculative exec while waiting for array1\_size:

- Predict that if() is true

- Read address (array1 base + x)

(using out-of-bounds x=1000)

- Read returns secret byte = 09 (in cache ⇒ fast )

#### Memory & Cache Status

array1\_size = 00000008

Memory at array1 base:

8 bytes of data (value doesn't matter)

Memory at array1 base+1000:

| 09 | F1 | 98 | CC | 90. | <br>(something secret) |

|----|----|----|----|-----|------------------------|

|    |    |    |    |     |                        |

| <u> </u>   |       |                  |                     |

|------------|-------|------------------|---------------------|

| array2[ 0* | 4096] |                  |                     |

| array2[ 1* | 4096] |                  |                     |

| array2[ 2* | 4096] |                  |                     |

| array2[ 3* | 4096] |                  |                     |

| array2[ 4* | 4096] |                  |                     |

| array2[ 5* | 4096] |                  |                     |

| array2[ 6* | 4096] | Contents don't r | natter              |

| array2[ 7* | 4096] | only care about  | cache <i>status</i> |

| array2[ 8* | 4096] | Uncached         | Cached              |

| array2[ 9* | 4096] | Uncacheu         | Cacilleu            |

| array2[10* | 4096] |                  |                     |

| array2[11* | 4096] |                  |                     |

| • • •      |       |                  |                     |

if (x < array1\_size)

y = array2[array1[x]\*4096];</pre>

Attacker calls victim with x=1000

Next:

- Request mem at (array2 base + 09\*4096)

- > Brings array2 [09\*4096] into the cache

- Realize if() is false: discard speculative work

proceed to next instruction

| Memory & Cache Status                                                 |  |  |  |  |  |  |

|-----------------------------------------------------------------------|--|--|--|--|--|--|

| array1_size = 00000008                                                |  |  |  |  |  |  |

| Memory at array1 base:                                                |  |  |  |  |  |  |

| 8 bytes of data (value doesn't matter)                                |  |  |  |  |  |  |

| Memory at array1 base+1000:                                           |  |  |  |  |  |  |

| <b>09</b> F1 98 CC 90 (something secret)                              |  |  |  |  |  |  |

| array2[ 0*4096]                                                       |  |  |  |  |  |  |

| array2[ 1*4096]                                                       |  |  |  |  |  |  |

| array2[ 2*4096]                                                       |  |  |  |  |  |  |

| array2[ 3*4096]                                                       |  |  |  |  |  |  |

| array2[ 4*4096]                                                       |  |  |  |  |  |  |

| array2[ 5*4096]                                                       |  |  |  |  |  |  |

| array2[ 6*4096] Contents don't matter                                 |  |  |  |  |  |  |

| array2[ 7*4096] only care about cache <i>statu</i><br>array2[ 8*4096] |  |  |  |  |  |  |

| array2[ 9*4096] Uncached Cached                                       |  |  |  |  |  |  |

| array2[10*4096]                                                       |  |  |  |  |  |  |

| array2[11*4096]                                                       |  |  |  |  |  |  |

if (x < array1\_size)

y = array2[array1[x]\*4096];</pre>

Attacker calls victim with x=1000

Attacker: (another process or core)

- for i=0 to 255: measure read time for array2[i\*4096]

- When i=09 read is fast (cached), reveals secret byte !!

- Repeat with many  $\times$  (10KB/s)

|                              |                                                                                                                                      | ,                                                  |                   |      |           |         |        |        |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-------------------|------|-----------|---------|--------|--------|

| arra                         | ay1_                                                                                                                                 | size                                               | =                 | 000  | 80000     |         |        |        |

| 8                            | Memory at array1 base:<br>8 bytes of data (value doesn't matter)<br>Memory at array1 base+1000:<br>09 F1 98 CC 90 (something secret) |                                                    |                   |      |           |         |        |        |

| arra<br>arra<br>arra<br>arra | .y2 [<br>.y2 [<br>.y2 [<br>.y2 [                                                                                                     | 0*409<br>1*409<br>2*409<br>3*409<br>4*409<br>5*409 | 96]<br>96]<br>96] |      |           |         |        |        |

|                              | _                                                                                                                                    | 6*409                                              |                   | ≻ Co | ntents o  | lon't i | matter |        |

| arra                         | y2 [                                                                                                                                 | 7*409                                              | 96]               | on   | ly care a | about   | cache  | status |

| arra                         | y2 [                                                                                                                                 | 8*409                                              | 96]               |      |           |         |        |        |

| arra                         | y2 [                                                                                                                                 | 9*409                                              | 6]                |      | Uncad     | ined    | Cad    | ched   |

|                              |                                                                                                                                      | 10*409                                             |                   |      |           |         |        |        |

|                              | -                                                                                                                                    | 11*409                                             |                   |      |           |         |        |        |

| •••                          | <u> </u>                                                                                                                             |                                                    | ,                 |      |           |         |        |        |

Memory & Cache Status

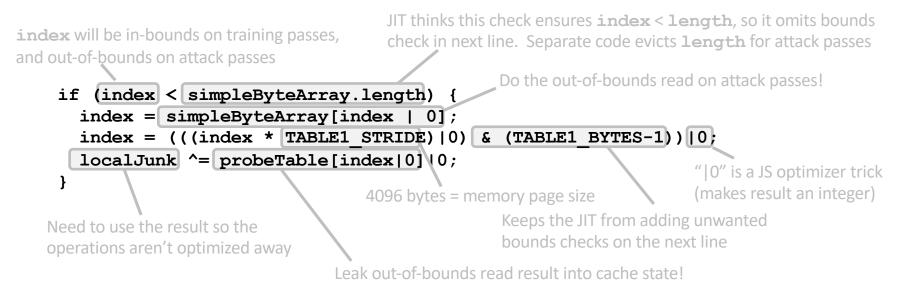

# Violating JavaScript's sandbox

- Browsers run JavaScript from untrusted websites

- JIT compiler inserts safety checks, including bounds checks on array accesses

- Speculative execution runs through safety checks...

Can evict length/probeTable from JavaScript (easy)

... then use timing to detect newly-cached location in probeTable

## Variant 2: indirect branches

Indirect branches: can go anywhere, e.g. jmp[rax]

- If destination is delayed, CPU guesses and proceeds speculatively

- Find an indirect jmp with attacker controlled register(s)

... then cause mispredict to a useful 'gadget' y = array2[array1[x]\*4096];

Attack steps:

- Mistrain branch prediction so speculative execution will go to gadget

- Evict address [rax] from cache to cause speculative execution

- **Execute** victim so it runs gadget speculatively

- **<u>Detect</u>** change in cache state to determine memory data

# Non-mitigations

Can we prevent Spectre without a huge cost in performance?

**Idea 1:** fully restore cache state when speculation fails.

Problem: Insecure!

Speculative execution can have observable side effects beyond the cache state

```

if (x < array1_size) {

y = array1[x];

do_something_observable(y);

}</pre>

```

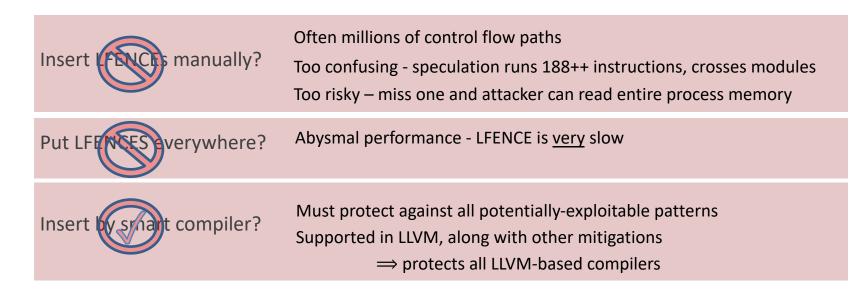

occupy a bus: detectable from another core, or cause EM radiation Variant 1 mitigation: Speculation stopping instruction (e.g. LFENCE)

• Idea: insert **LFENCE** on <u>all</u> vuln. code paths

if (x < array1\_size)

LFENCE // processor instruction

y = array2[ array1[x]\*4096 ];</pre>

Variant 1 mitigation: Speculation stopping instruction (e.g. LFENCE)

• Claim: efficient, no performance impact on benchmark software

Transfer of blame (CPU -> SW): "you should have put an LFENCE there"

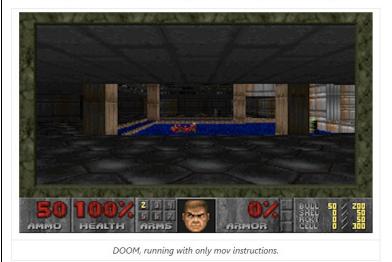

# Mitigations: Indirect branch variant

#### Remove all branches?

#### DOOM with no branches:

• One frame every ~7 hours

#### A branchless DOOM

This directory provides a branchless, mov-only version of the classic DOOM video game.

This is thought to be entirely secure against the Meltdown and Spectre CPU vulnerabilities, which require speculative execution on branch instructions.

#### Oops! Variant 4: speculative store

### Mitigations: summary

Mitigations are messy for all Spectre variants:

- Software must deal with microarchitectural complexity

- Mitigations for all variants are really hard to test:

- active area of research

### More ideas needed !

## ... but there is more

More speculative execution attacks:

- Meltdown

- Rogue inflight data load (**RIDL**) and **Fallout**

- ZombieLoad

- Store-to-leak forwarding

- Micro-op caches (June 2020)

Enable reading unauthorized memory (client, cloud, SGX)

• Mitigating incurs significant performance costs

# How to evaluate a processor?

Processors are measured by their performance on benchmarks:

- Processor vendors add <u>many</u> architectural features to speed-up benchmarks

- Until recently: security implications were secondary

⇒ lots of security issues found in last four years

... likely more will be found in coming years

### THE END